طراحی سریال ساز / عکس سریال ساز BUSLVDS برای ایستگاه های پایه ۳G

۹,۹۰۰ تومان

محصول با کیفیت

پرداخت امن و آنلاین

دانلود پس از پرداخت

ضمانت بازگشت وجه

طراحی سریال ساز / عکس سریال ساز ۶۶۰Mbps BUSLVDS تا ۱۰۰Mbs برای ایستگاه های پایه ۳G.

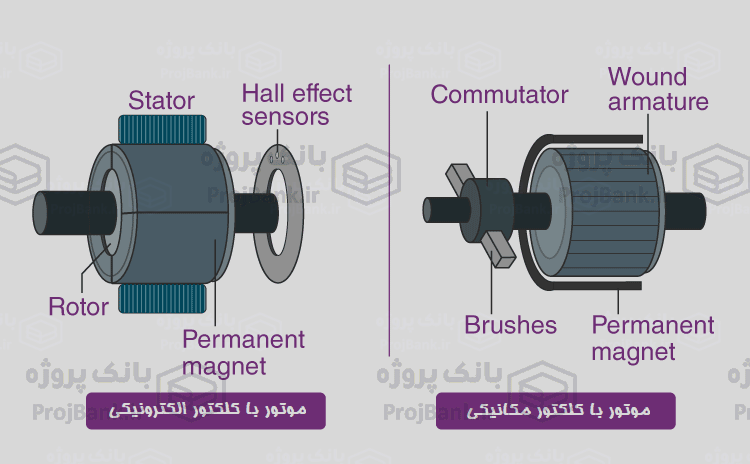

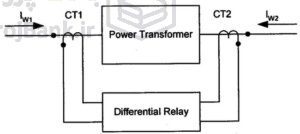

این مقاله اجرای BULVDS SERDES را برای ایستگاه های پایه ۳G نشان میدهد. این سریال ساز / عکس سریال ساز SERDES از یک PLL مجتمع شده کامل با رنج گسترده کاری و یک DLL دیجیتال براساس تصحیح ساعت و تاریخ استفاده میکند (CDR).

کاربرد مجموعه تراشه ابتدا با جزئیات طراحی هر بلوک اصلی برای این SERDES تعریف شده است. این مقاله میخواهد چند دیدگاه برای اجرای این چنین LVDS SERDES فراهم کند تا قابلیت بیشتری برای انتقال قوی داده در ایستگاههای اصلی ۳G فراهم سازد.

مقدمه

ارتباطات سیال ۳G مانند EDGE, W-CDMA و CDMA 2000 و عده فراوانی media (مسیر) به دسترسی به اینترنت سرعت بالا با استفاده از تلفنهای سلولی. ایستگاههای بافت سلولی نیاز به پردازش توزیع نمایی مقادیر زیادی از داده دیجیتال دارد.

حداقل سازی فضا، نویز و مصرف توان و لذا کاهش هزینه [۱۳t2]. هنگامی که LVDS برای ارتباطات نقطه به نقطه طراحی شده که دارای توازن بیشتر و مسیر امپدانس کنترل شده ۱۰۰ اهمی، تکنولوژی باس (VDS (BLVDS)) که برای کابل چند نقطهای و کاربردهای سطح پشتی بهینه شده است.

آن با LVDS استاندارد در ایجاد جریان راه اندازی افزوده شده برای جابجایی خروجیهای دوبل که در کاربرد چند نقطهای مورد نیاز هستند فرق میکند. در این مقاله، طراحی چنین BLVDS SERDES ایستگاه های پایه ۳G بحث خواهد شد. این دو تراشه BLVDS SERDES

SN6SLV1021/1212(100Mbps ~ 400Mbps)

و

SN6SLV1023/1224(300Mbps ~ 660Mbps) می توانند هر دو در ترکیب باس شکل ۱ بکار روند.

شکل ۱٫ ترکیبات باس: نقطه به نقطه، چند قطرهای و چند نقطهای

معماری باس LVDS SERDES

معماری BLVDS SERDES در زیر در شکل [۴][۳]۲ نشان داده شده است. آن یک ۱۰:۱ SERDES TX/RX است. توابع سری ساز با ایجاد یک PLL مجتمع برای سری سازی یک شاخه گسترده داده ده بیتی CMOS/TTL به یک شاخه داده یک بیتی سرعت بالای LVDS آن سوی صفحه پشتی یا کابل بکار میرود هنگامی که دو بیت ساعت برای شکل گیری (استارت بیت ۱ و توقف بیت ۰) بکار میرود.

عکس سری ساز تابع معکوس را با استفاده از ساعت تصحیح شده برای عکس سری سازی داده ورودی و آشکار سازی چارچوب اطلاعات انجام میشود. در سریال ساز و عکس سریال ساز یک مدار مجتمع کامل PLL میخواهد. در سریال ساز به PLL به عنوان مولد ساعت انتقال بکار میرود در حالی که در عکس سریال ساز، PLL قسمتی از تصحیح ساعت و تاریخ (CDR) است.

مداری که اطلاعات بکار رفته ساعت را در ورود شاخه اطلاعات بر میگزیند.

شکل.۲ بلوک دیاگرام سیستم سریال ساز (TX)/عکس سریال ساز (RX)

بخشهای زیر ابتدا در مورد PLL بحث میکنند که بحرانی ترین بلوک در هر SERDES است. لذا طراحی درایور BLVDS روی TX تعریف خواهد شد. در RX اجرای مدار CDR کار اصلی طراحی است و لذا آشکار خواهد شد.

طراحی PLL

PLL مورد استفاده در این SERDES یک نسبتاً حوضه گسترده عملیاتی دارد. اگر نرخ عبارت موازی از MHz66 تا MHz10 باشد، نرخ خط داده از Mbps100 تا Mbps66 خواهد بود. با ملاحظه بیت شروع و پایان، به طور متعادل نرخ خط بایستی از Mbps120 تا Mbps792 باشد.

به منظور کاهش مصرف توان مثل تولید عامیانه، یک تکنیک نمونه گیری دوبل برای پایین آوردن ساعت بیت سرعت بالا روی تراشه در TX و RX بکار میرود.

اگر ساعت بایت از ASIC بیاید TCLK است. فرکانس ساعت بیت در ۶TCLK است. با کرد در نصف نرخ، نوسان ساز برای کارکردن از MHz60 تا MHz396 نیاز دارد.

نوسان ساز زنگ شش حالته بر اساس سلول تأخیر بار هم زمان است که در [۵] اشاره شده برای پوشش رنج سرعت زیر گوشههای مختلف پروسه بکار میرود. این سلول تأخیر بار متوازن برا داشتن رنج تأخیر خیلی گسترده ادعا میکند.

تعداد صفحات : ۱۱

نوع فایل : ورد ۲۰۰۳ (.doc)

فاقد شکل

پرفروش ترین ها

طرح توجیهی ساختمان سازی + فرمول تبدیل قیمت

جزوه اصول سیستم های قدرت + نمونه سوال و پاسخنامه

محصولات مرتبط

شما اینجا هستید :

برای استفاده از مطالب بانک پروژه ، ذکر منبع الزامی است. تمام حقوق این سایت مربوط به بانک پروژه است.

طراحی سایت و توسعه وردپرس توسط نادر حاجی حیدری

نقد و بررسیها

هنوز بررسیای ثبت نشده است.